前言

- 工程师可以实现跨芯片、封装和电路板并行设计,从而节省时间并最大程度地减少错误

- 非常适合集成多种结构电路类型(包括射频、模拟和数字系统)的设计

Cadence® Virtuoso® System Design Platform 整合了两项世界一流的 Cadence 技术——定制化集成电路设计技术和封装/PCB 设计/分析技术,由此创建了一套方法,使得多芯片异构系统的设计和验证流程更简单、流畅以及自动化。

利用 Virtuoso Schematic Editor 和 Virtuoso Analog Design Environment,为集成电路和封装/系统级的电路图设计输入、分析和验证提供了单一的平台环境。此外,Virtuoso System Design Platform 为与 Cadence SiP 应用环境和Clarity 3d Solver 提供了自动化双向对接界面。

Virtuoso System Design Platform 使集成电路设计人员能够轻松地在集成电路验证流程中纳入系统级布线寄生效应,将封装/电路板版图连线数据与集成电路版图的寄生效应电气模型结合在一起,从而节省时间。之后使用自动生成的“系统级”原理图来轻松创建用于最终电路级仿真的仿真电路。Virtuoso System Design Platform 使系统级仿真流程实现了自动化,集成电路设计人员无需再将系统级布线寄生效应模型手动集成,避免了错误发生。

集成异构系统

如今许多模拟、射频和混合信号设计都需要在不同的衬底工艺类型上集成多个集成电路,以实现所需的性能目标。异构系统的集成使设计人员可以获得使用单片集成电路(系统级芯片)设计方法无法轻松实现的结果。同时,异构集成也为当今的设计师带来了一系列全新的挑战。

系统级封装 (SiP) 是将混合工艺集成到单个设计中的最常用方法之一。使用这种方法时,集成电路与封装基板设计团队需要能够无缝运用一套集成的工具流程。为了应对这一挑战,Virtuoso System Design Platform 提供了一种新颖的跨平台解决方案,可简化和自动化具有基于不同制程设计套件 (PDK) 的片外系统和多个集成电路的封装/模块的设计。

下载地址

百度网盘:https://pan.baidu.com/s/1WZPpD3qMKwnlUcbYNTXqMg?pwd=sgbt

其他下载:http://ali.kn21.xyz/s/3922bc51-1637-4adc-9be1-6d2e96598222

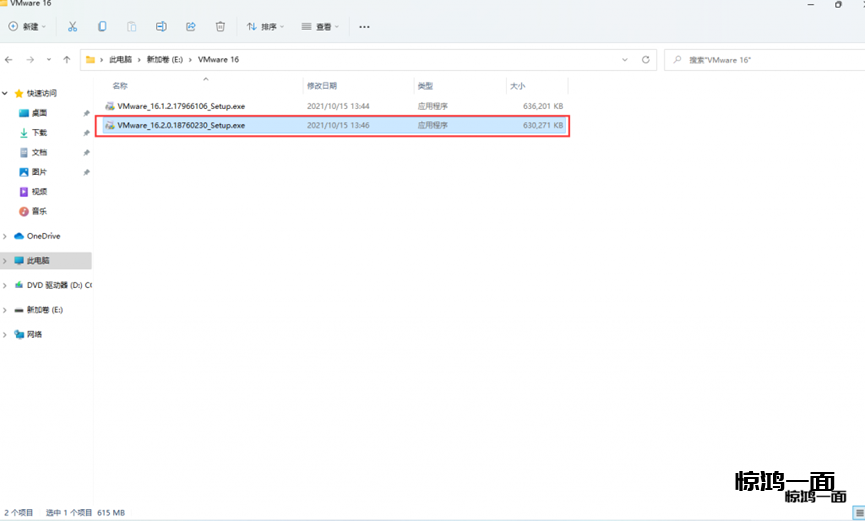

1. 下载安装包并解压出来,选择一个版本运行,这里我选择 VMware_16.2.0.18760230_Setup。

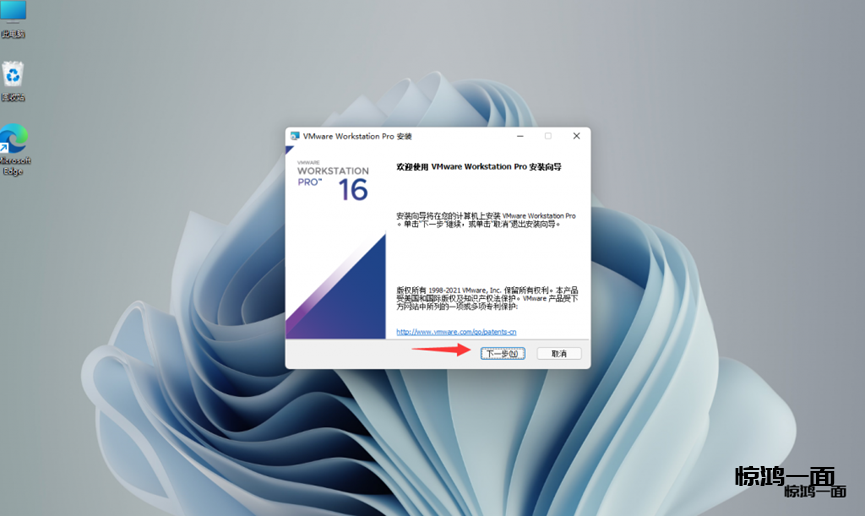

2. 下一步

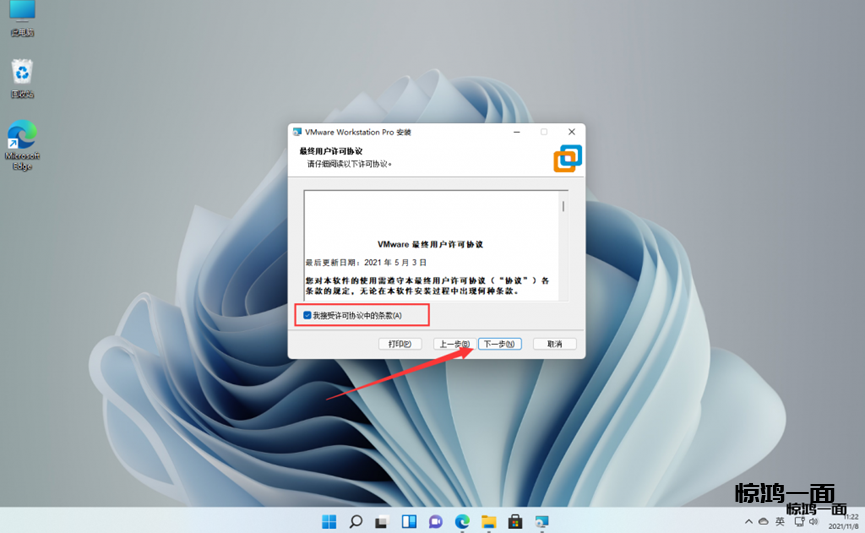

3. 勾选同意协议,下一步。

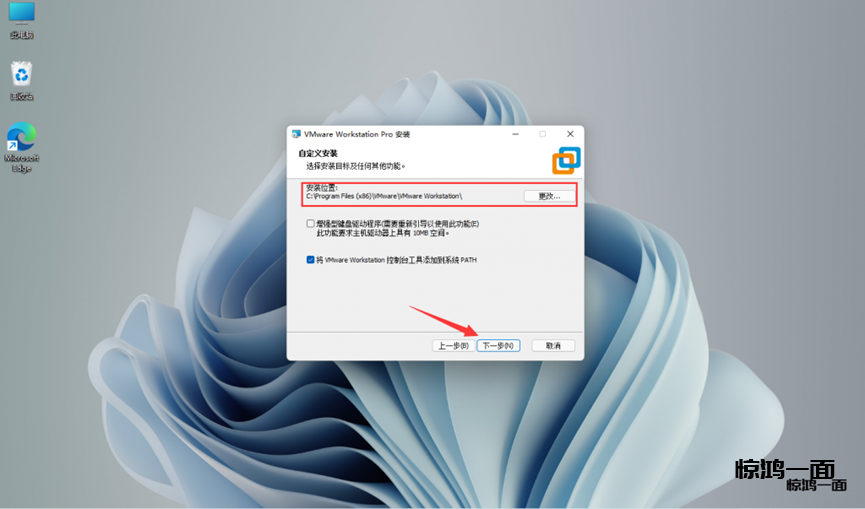

4. 更改安装位置,再下一步

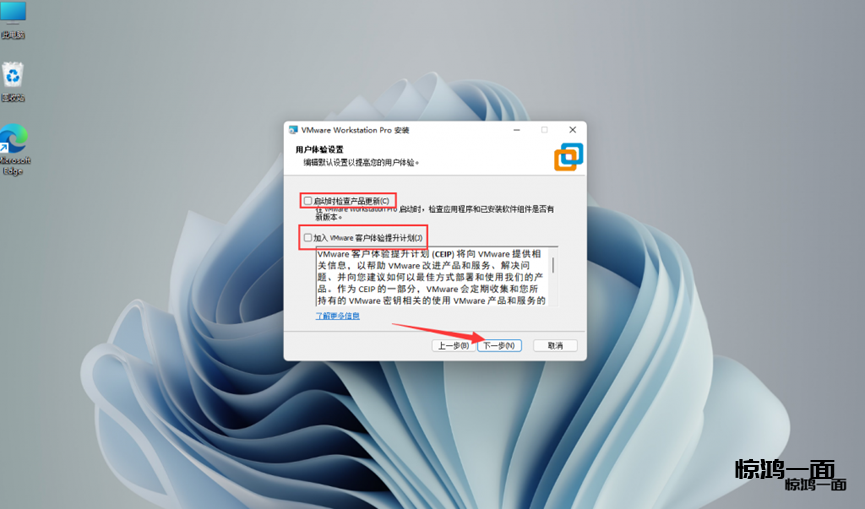

5. 按需求可取消勾选,再下一步

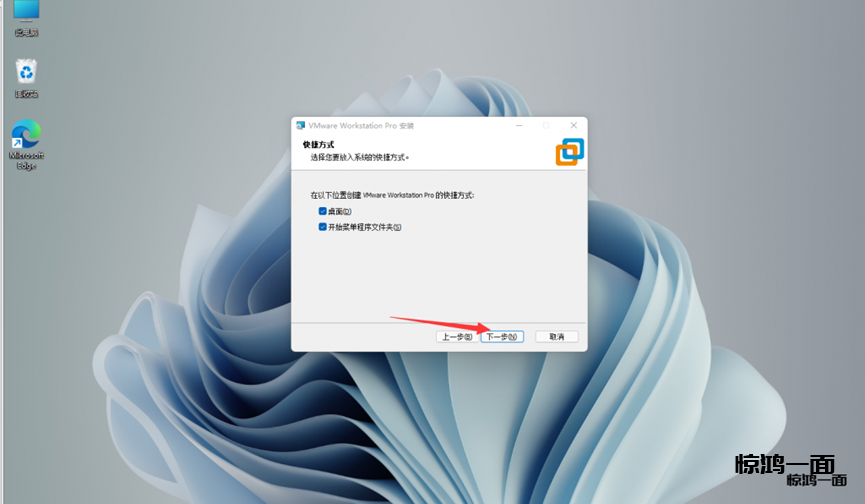

6. 下一步

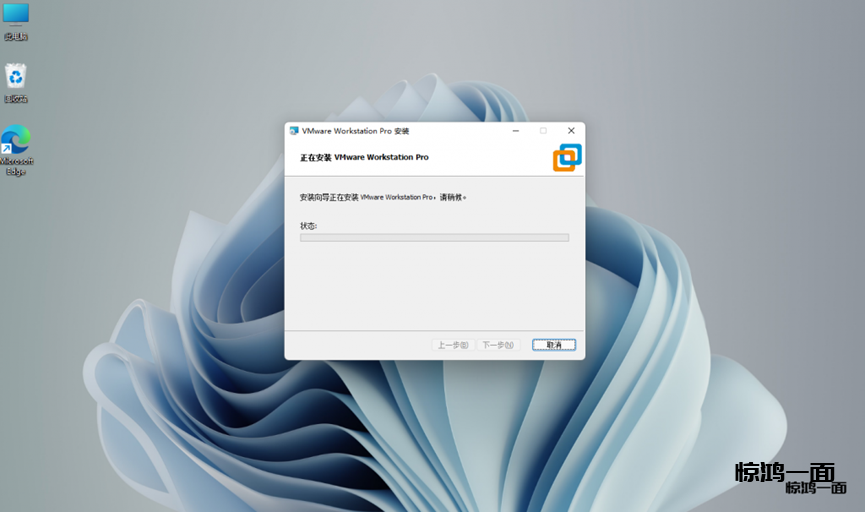

7. 安装中等待结束。

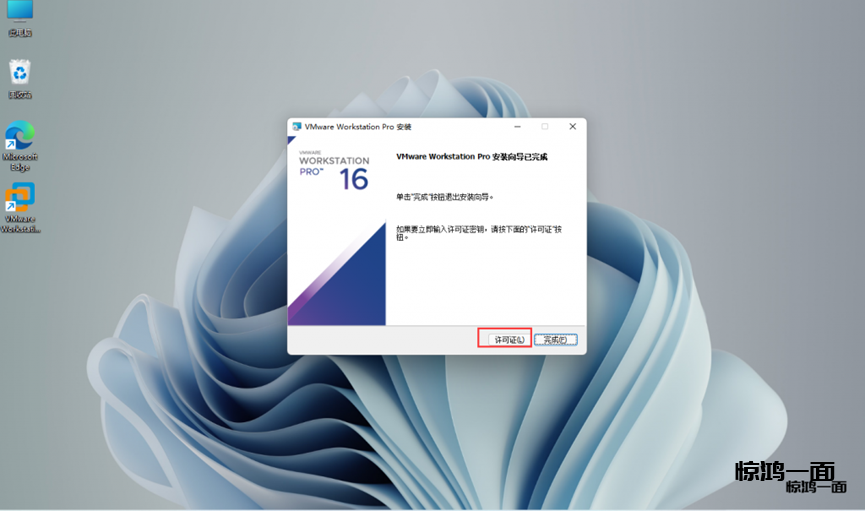

VMware Workstation 16 Pro激活教程

1. 点击许可证

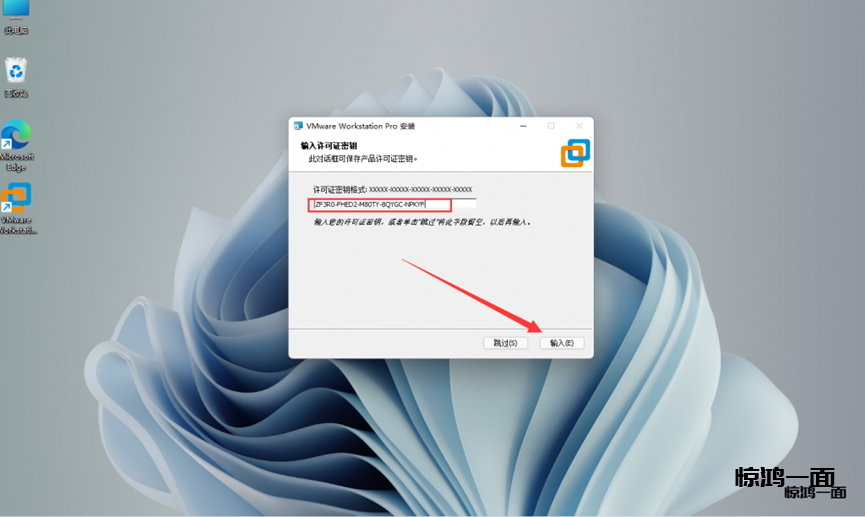

2. 任意输入一组许可证

ZF3R0-FHED2-M80TY-8QYGC-NPKYF

YF390-0HF8P-M81RQ-2DXQE-M2UT6

ZF71R-DMX85-08DQY-8YMNC-PPHV8

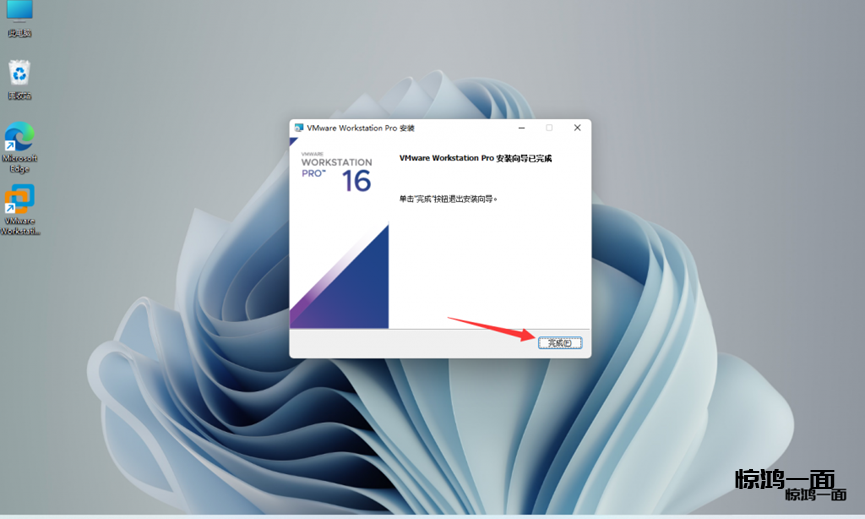

3. 完成

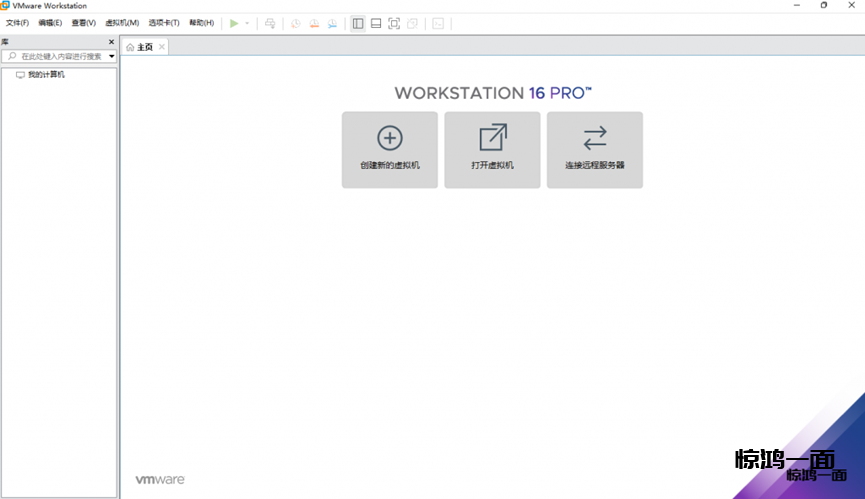

4. 回到桌面运行

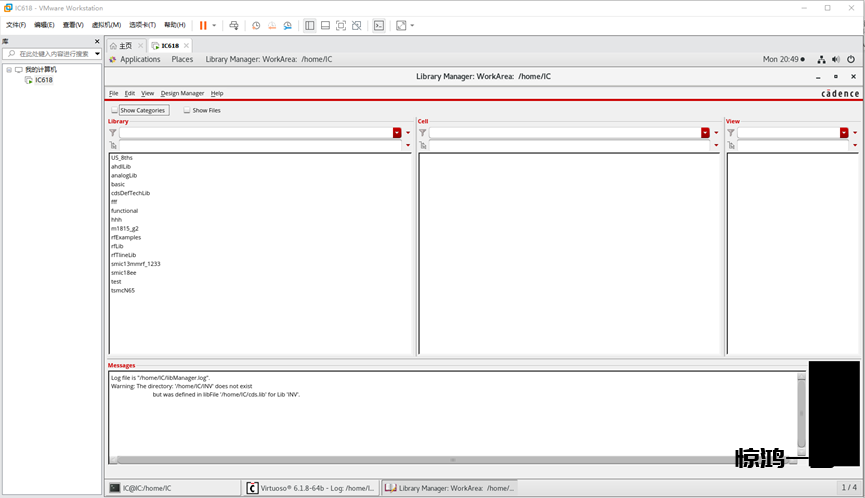

Cadence IC618 Virtuoso安装教程

1.载好虚拟机镜像,并解压

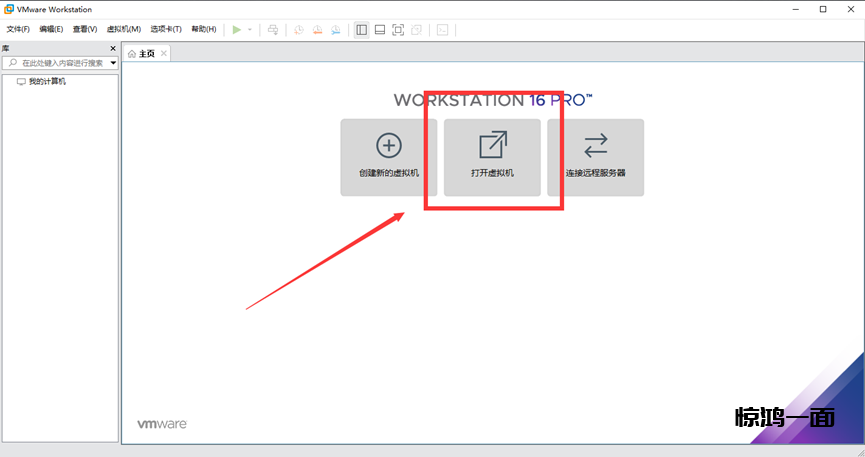

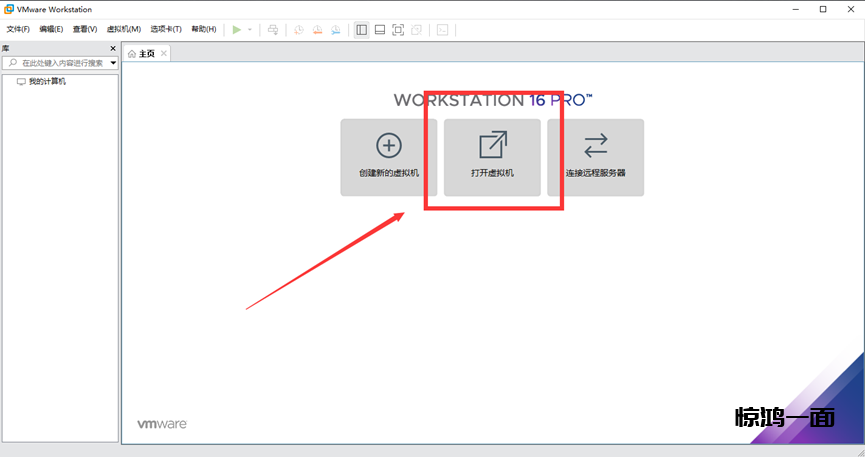

2.回到虚拟机操作界面,点击打开虚拟机

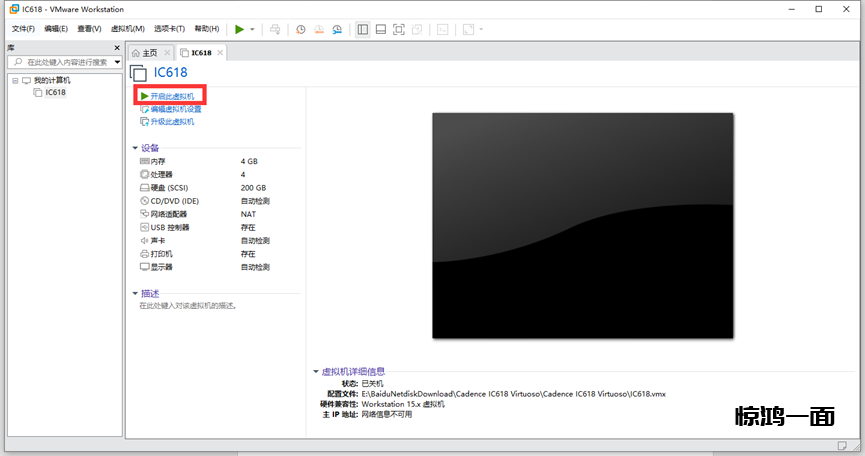

4.开启虚拟机

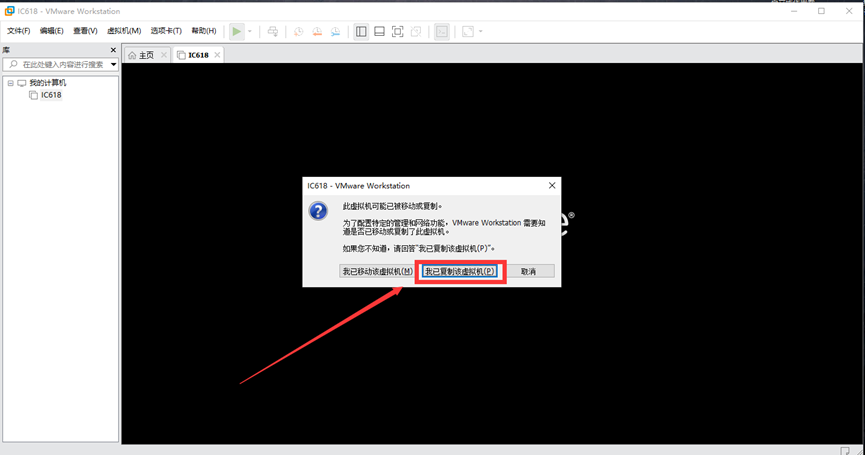

5.选择我已复制虚拟机

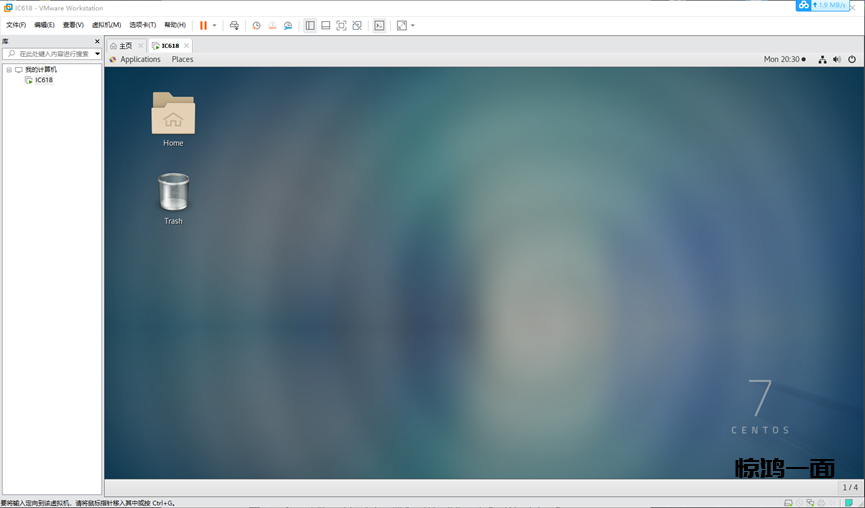

6.进入界面

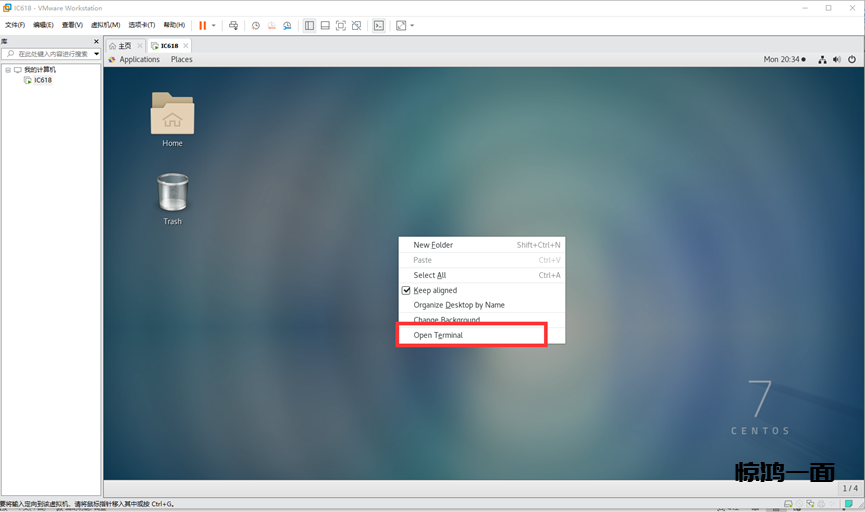

7.右键选择Open Terminal

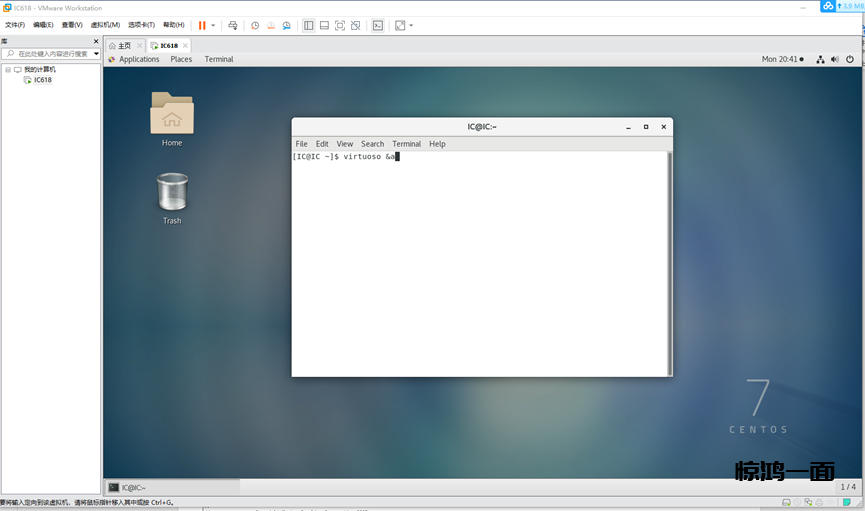

8.输入virtuoso &运行

9.完成